文|半導體產業縱橫

摩爾定律接近極限,但魅力卻無限。從14nm、7nm再到如今的3nm、2nm,國際大廠對摩爾定律的追求幾近巔峰。

圍繞3nm節點,全球巨頭們的競賽堪稱激烈。但3nm這一節點呈現了不同的特征,這個節點的研發和生產的成本極高,這也增加了供應商和客戶的風險,所有的玩家極力地在先進技術與成本之間尋求平衡。

在這場巨頭競爭的背后,真正的客戶市場在哪里?又或者說,為什么沒客戶?

3nm競爭

臺積電

2016年9月,臺積電董事長劉德音首次透露了3nm制程的進度,他表示,目前組織了300-400人的團隊研發中。

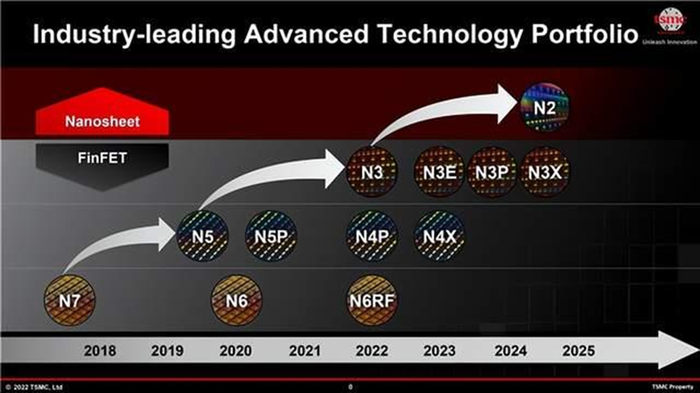

在2022 年的技術研討會上,臺積電分享了有關其即將推出的 3nm節點的一些細節。臺積電的第一個 3nm節點是“N3”節點。該節點于2018-2019 年宣布,計劃于今年下半年發布。

三星

2018年,三星電子在位于美國的2018年三星半導體代工論壇上,公布其全面的芯片制程技術路線圖,其中包括5nm、4nm、3nm三個先進制程。

今年6月30日,三星宣布成為全球首家已經開始量產3nm制程芯片的廠商。三星表示其初代3nm制程比起5nm 產品功耗降低45%、效能提升16%、節點面積減少16%;第二代3nm制程更會降低50% 功耗、擁有30% 效能提升,并減少35%節點面積。

英特爾

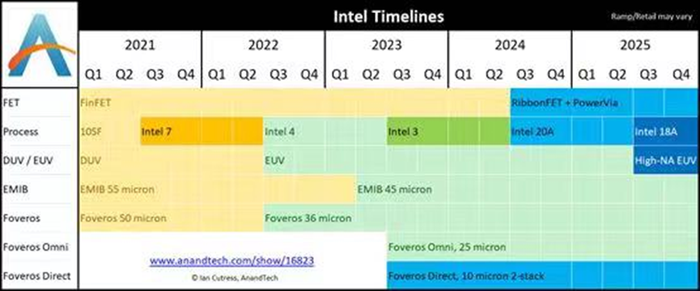

在3nm制程上,英特爾同樣在布局。英特爾為其制程節點引入了全新的命名體系,市面上來說,Intel 3相當于其他廠商的3nm制程。

根據英特爾的制程路線圖來看,Intel 3會在Intel 4之后亮相。在“英特爾加速創新”線上發布會上,英特爾計劃Intel 3 將在2023年下半年亮相。

3nm誰在用?

一般來說,芯片的性能與晶體管數量有關,但考慮到芯片的功耗、面積不能過高,那么提升芯片性能的最好辦法就是縮小微電子元件和電路的體積以及它們之間的距離,這樣在芯片面積不變的情況下可以塞入更多的晶體管數量,性能自然更強。

相比于電腦、汽車這些產品,手機的體積相當小,會拿在手上使用,并且為了方便使用時也會脫離電源。這意味著除了性能之外,手機還得考慮續航能力和手機溫度。而作為耗電大戶和發熱大戶的芯片,在用上新制程的情況下不僅能夠提高性能,還能降低功耗,減少發熱,提高用戶的使用體驗,這樣的誘惑對于任何一家手機廠家都是無法拒絕的。而且現在芯片制程也成為了手機的賣點之一,所以手機都在搶著用新制程。同理還有其他便攜類產品也都是使用先進制程的預備軍。

但是不是所有的手機都能用3nm的,蘋果作為臺積電最大客戶,將率先嘗鮮新工藝,據傳M2 Pro就將基于3nm工藝打造。M2 Pro就是蘋果推出的筆記本電腦,但是除此之外,沒有消息有其他品牌或者其他產品有使用3nm的消息。

其他手機為什么沒有用呢?不用最先進的3nm是否意味著手機就是落后的呢?

3nm工藝確實能顯著提升手機芯片的性能及能耗,但目前的手機處理器的性能早已嚴重過剩,堆砌更多的性能也難以發揮利用。而且實際上手機芯片并不是一直處于峰值性能狀態,幾乎所有手機都會加入溫度控制模塊,在檢測到溫度過高時會降低芯片性能減少發熱量。一味地追求工藝制程的進步,其實只是讓紙面數據看起來更華麗一些,并不能為用戶的實際體驗帶來多大的提升。并且,處理器使用更先進的工藝制程,也意味著其制造成本更高,手機的價格也就更貴,這部分代價都需要消費者去承擔。

所以3nm在唯一的客戶這里,也是“岌岌可危”的。果不其然,8月底有消息稱臺積電內部已經決定放棄 N3 工藝,因為客戶幾乎都不愿意用,包括蘋果。

無路可“用”的3nm

車企:缺芯,但缺的不是3nm

車企先鋒特斯拉現在的HW3.0內部最先進的芯片制程工藝也僅僅為14nm,手機行業7nm都是四年前的事情了,被稱為現代工業皇冠的汽車,其使用最先進的芯片卻如此“落后”,甚至比一臺才幾千元的手機所用的芯片還要“落后”?

簡單來說是三個方面的原因:汽車內部有著廣闊的空間,芯片面積不太過于限制;芯片發熱不用擔心;功耗在汽車本身的耗能面前很小,汽車也不擔心功耗。

以及汽車的使用場景相對固定,基本上就是簡單的顯示車輛信息、設置、地圖、音樂、視頻等場景,對芯片性能要求相對不高。并且現在各大車企推出的智能座艙并沒有多少能夠自由安裝軟件,更別說安裝游玩原神這類對性能要求極高的游戲,而車機的位置、大小也在使用車機玩游戲這件事情顯得不那么現實。

所以汽車行業不需要太先進的芯片。他們缺的,其實是那些技術成熟甚至稱得上 “老舊”的基礎型芯片。比如ESP芯片,130nm制程,17年前的技術,但現在奇缺,因為沒多少人愿意生產那么老的芯片。純電動車的電池管理芯片IGBT,65nm制程,現在也缺的很,也是因為沒多少廠家還保存著那么老的生產線。

所以現在的情況是這些被芯片行業視為老古董的芯片直接拖住了全球汽車行業的產能,缺芯并不缺3nm。

不需要還是用不起?

3nm代表著摩爾定律已經達到了極限,但是無論是設計公司、制造廠還是封裝廠,對于先進制程研發都從未停止,巔峰依舊是他們永遠的追求,先進制程依然是關乎產業命脈、國家安全的關鍵,未來科技為王,落后就要挨打。3nm的應用少不是唱衰,而是另有原因?

貴,太貴

國際商業戰略公司 (IBS) 首席執行官Handel Jones表示:“設計28nm芯片的平均成本為4000萬美元。相比之下,設計7nm芯片的成本為2.17億美元,設計5nm設備的成本為 4.16億美元,3nm設計更是將耗資高達5.9億美元。”

在先進工藝設計成本上,半導體技術研究機構Semiengingeering也統計了不同工藝下芯片所需費用,其中28nm節點上開發芯片只要5130萬美元投入,16nm節點需要1億美元,7nm節點需要2.97億美元,到了5nm節點,開發芯片的費用將達到5.42億美元,3nm節點的數據還沒有,大概是因為3nm現在還在研發階段,成本不好估算。但從這個趨勢來看,3nm芯片研發費用或將接近10億美元。

如此高昂的成本,是大廠都無法承受的。2018 年,因高昂的研發成本,當時排名世界第二的代工廠格羅方德被迫放棄7nm制程的研發。目前,全球唯有臺積電、三星、英特爾還在向3nm、2nm峰頂沖刺。

貴不僅僅是研發貴,貴在整個生產鏈。首先是晶圓代工成本,根據CEST的模型,在5nm節點上構建的單個300mm晶圓的成本約為16988美元,在7nm節點上構建的類似晶圓成本為9346美元。可以看到,相同尺寸晶圓,5nm工藝節點相比7nm每片晶圓代工售價高7000多美元。從中可以推斷出,在3nm節點上構建的晶圓成本或將達到3萬美元左右,晶圓代工成本將進一步提高。

其次是掩膜成本,臺積電從10nm到5nm,隨著EUV光刻技術的應用,掩膜使用數量有所減少,5nm與10nm制程中掩膜使用數量相差不多。但是,在掩膜數量基本持平的情況下,更先進的制程工藝使得掩膜總成本提升,能側面反映出掩膜平均成本在不斷升高。而ASML第二代EUV光刻機價格預計將突破3億美元。

最后還有昂貴的研發和人力費用。人才缺失是這個行業永遠的熱門話題。

臺積電也撐不住了?

N3為什么變成了N3E?前不久臺積電技術研討會上的大部分消息都是關于 N3E 的,而最初的 N3 節點只是經過簡短的提及。

N3 是臺積電第一代 3nm 工藝,相比N5 工藝功耗可降低約 25-30%,性能可提升 10-15%,晶體管密度提升約 70%。但是N3 工藝應用范圍較窄,只適合制造特定的產品,面向超強投資能力、追求新工藝的早期客戶。就是太貴了,只適合愿意燒錢的蘋果、英特爾,結果這兩家已經不用了。

Wikichip更是直言:“N3節點很奇怪。”它看起來似乎是臺積電放棄的一次性節點。是不是臺積電工程師在此制程中遇到了一些障礙,并決定中途改變,變成了N3E呢?N3E被納入臺積電的傘式營銷“N3家族”,但N3E 與 N3 非常不同。據說設計規則非常不同,并且 IP 的實現方式不同,足以使它們在設計方面不兼容。對于客戶而言,也沒有直接的 IP 遷移路徑可讓在 N3 上制作的設計遷移到 N3E。這次可以相信嗎?蘋果明年會用嗎?臺積電3nm的籃子里也只有蘋果一顆“蛋”。

摩根大通在最新發布的報告中指出,臺積電面臨聯發科、AMD、高通、英偉達等四大先進制程客戶砍單,計劃關閉4臺極紫外光(EUV)光刻機以減少產出,屆時月產能將銳減1.5萬片,明年獲利恐衰退8%,是三年來首度面臨獲利下滑。據了解,臺積電目前擁有大約80臺EUV光刻機,主要用于7nm、5nm及以下的先進工藝,后續還會量產3nm工藝。然而隨著PC、手機、顯卡等產品的需求量下滑,所需的芯片數量勢必會受到影響。蘋果3nm跳單是不是也影響到了臺積電呢?

總而言之,今年的3nm缺少了天時、地利、人和,未來不知道它能不能走出“水逆”,我們翹首以待,靜觀其變。